Difference between revisions of "MBC2"

(Initial Revision :)) |

(No difference)

|

Revision as of 02:26, 23 June 2015

Nintendo's MBC2 can be used to address up to 2 Mbit of ROM and 512×4 bit of internal RAM.

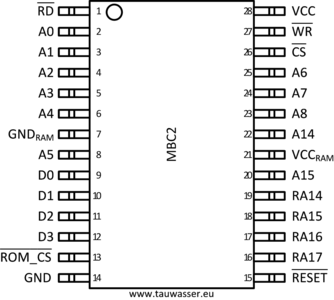

Pinout

| Pin No. | Name | Type | Comment |

|---|---|---|---|

| 28 | VCC | PWR | I/O 5V supply |

| 14 | GND | PWR | I/O Ground supply |

| 21 | VCC_RAM | PWR | RAM supply |

| 7 | GND_RAM | PWR | RAM Ground supply |

| 12Template:Ndash9 | D3Template:NdashD0 | I/O | Data Bus |

| 1 | RD | I | Low-Active Read Enable |

| 27 | WR | I | Low-Active Write Enable |

| 26 | CS | I | Low-Active Chip Select |

| 15 | RESET | I | Low-Active Asynchronous Reset |

| 20, 22Template:Ndash25, 8, 6Template:Ndash2 | A15Template:NdashA14, A8Template:NdashA0 | I | Address Bus |

| 16Template:Ndash19 | RA17Template:NdashRA14 | O | Upper ROM Address Lines |

| 13 | ROM_CS | O | Low-Active ROM Chip Select |

Footprint: SOP127P1200X225-24

Remarks: All I/O pins are protected via diodes to VCC/GND. VCC and VCC_RAM both supply RAM -- probably depending on VCC voltage.

Registers

Write-Accessible Registers:

- 0b00-- ---0 ---- ----: RAM Enable register

- 0b00-- ---1 ---- ----: ROM Bank register

- 0b10-- ---a aaaa aaaa: Internal RAM

RAM Enable Register

XX XX XX XX D3 D2 D1 D0 0x00 @ reset

\_________/

\-------- RAM Enable

A value of 0x0A enables RAM access, all other values disable RAM access.

ROM Bank Register

XX XX XX XX D3 D2 D1 D0 0x00 @ reset

\_________/

\-------- ROM Bank

ROM Bank selects which bank is mapped to 0x4000-0x7FFF. The written value is zero-adjusted before output on RA17Template:NdashRA14.

Behavior

TODO