Difference between revisions of "MBC1"

m (→Pinout) |

(→Pinout) |

||

| Line 7: | Line 7: | ||

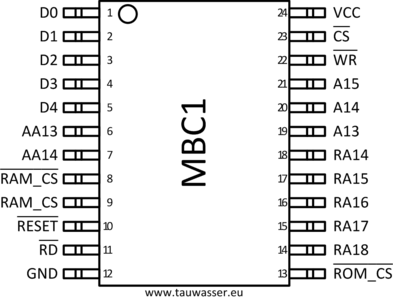

[[Image:MBC1 Pinout.png|center|x300px]] | [[Image:MBC1 Pinout.png|center|x300px]] | ||

| − | {| class="wikitable" style="margin:1em auto; | + | {| class="wikitable pintable" style="margin:1em auto; width: 66%;" |

| − | !style="width: 20%;" | | + | !style="width: 10%;" | Pin No. |

| − | !style="width: | + | !style="width: 20%;" | Name |

| + | !style="width: 10%;" | Type | ||

!style="width: 60%;" | Comment | !style="width: 60%;" | Comment | ||

|- | |- | ||

| − | |D4 | + | |28 |

| + | |VCC | ||

| + | |PWR | ||

| + | |5V supply | ||

| + | |- | ||

| + | |14 | ||

| + | |GND | ||

| + | |PWR | ||

| + | |Ground supply | ||

| + | |- | ||

| + | |5{{ndash}}1 | ||

| + | |D4{{ndash}}D0 | ||

|I | |I | ||

|Data Bus | |Data Bus | ||

|- | |- | ||

| + | |11 | ||

|{{Overline|RD}} | |{{Overline|RD}} | ||

|I | |I | ||

|Low-Active Read Enable | |Low-Active Read Enable | ||

|- | |- | ||

| + | |22 | ||

|{{Overline|WR}} | |{{Overline|WR}} | ||

|I | |I | ||

|Low-Active Write Enable | |Low-Active Write Enable | ||

|- | |- | ||

| + | |23 | ||

|{{Overline|CS}} | |{{Overline|CS}} | ||

|I | |I | ||

|Low-Active Chip Select | |Low-Active Chip Select | ||

|- | |- | ||

| + | |10 | ||

|{{Overline|RESET}} | |{{Overline|RESET}} | ||

|I | |I | ||

|Low-Active Asynchronous Reset | |Low-Active Asynchronous Reset | ||

|- | |- | ||

| − | |A15 | + | |21{{ndash}}19 |

| + | |A15{{ndash}}A13 | ||

|I | |I | ||

|Address Bus | |Address Bus | ||

|- | |- | ||

| − | |RA18 | + | |18{{ndash}}14 |

| + | |RA18{{ndash}}RA14 | ||

|O | |O | ||

|Upper ROM Address Lines | |Upper ROM Address Lines | ||

|- | |- | ||

| − | |AA14 | + | |7{{ndash}}6 |

| + | |AA14{{ndash}}AA13 | ||

|O | |O | ||

|Upper ROM/RAM Address Lines | |Upper ROM/RAM Address Lines | ||

|- | |- | ||

| + | |8 | ||

|{{Overline|RAM_CS}} | |{{Overline|RAM_CS}} | ||

|O | |O | ||

|Low-Active RAM Chip Select | |Low-Active RAM Chip Select | ||

|- | |- | ||

| + | |9 | ||

|RAM_CS | |RAM_CS | ||

|O | |O | ||

|High-Active RAM Chip Select | |High-Active RAM Chip Select | ||

|- | |- | ||

| + | |13 | ||

|{{Overline|ROM_CS}} | |{{Overline|ROM_CS}} | ||

|O | |O | ||

Revision as of 23:03, 26 May 2015

MBC1

Pinout

| Pin No. | Name | Type | Comment |

|---|---|---|---|

| 28 | VCC | PWR | 5V supply |

| 14 | GND | PWR | Ground supply |

| 5Template:Ndash1 | D4Template:NdashD0 | I | Data Bus |

| 11 | RD | I | Low-Active Read Enable |

| 22 | WR | I | Low-Active Write Enable |

| 23 | CS | I | Low-Active Chip Select |

| 10 | RESET | I | Low-Active Asynchronous Reset |

| 21Template:Ndash19 | A15Template:NdashA13 | I | Address Bus |

| 18Template:Ndash14 | RA18Template:NdashRA14 | O | Upper ROM Address Lines |

| 7Template:Ndash6 | AA14Template:NdashAA13 | O | Upper ROM/RAM Address Lines |

| 8 | RAM_CS | O | Low-Active RAM Chip Select |

| 9 | RAM_CS | O | High-Active RAM Chip Select |

| 13 | ROM_CS | O | Low-Active ROM Chip Select |