Difference between revisions of "MBC1"

(Add MBC1) |

m (→Pinout) |

||

| Line 26: | Line 26: | ||

|{{Overline|CS}} | |{{Overline|CS}} | ||

|I | |I | ||

| − | |Low-Active | + | |Low-Active Chip Select |

|- | |- | ||

|{{Overline|RESET}} | |{{Overline|RESET}} | ||

Revision as of 19:58, 26 May 2015

MBC1

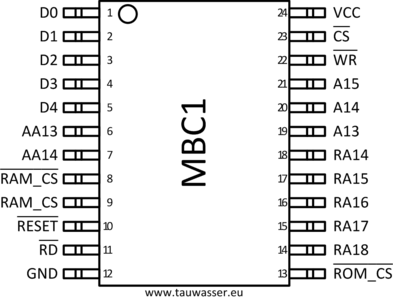

Pinout

| Pin | Direction | Comment |

|---|---|---|

| D4..D0 | I | Data Bus |

| RD | I | Low-Active Read Enable |

| WR | I | Low-Active Write Enable |

| CS | I | Low-Active Chip Select |

| RESET | I | Low-Active Asynchronous Reset |

| A15..A13 | I | Address Bus |

| RA18..RA14 | O | Upper ROM Address Lines |

| AA14..AA13 | O | Upper ROM/RAM Address Lines |

| RAM_CS | O | Low-Active RAM Chip Select |

| RAM_CS | O | High-Active RAM Chip Select |

| ROM_CS | O | Low-Active ROM Chip Select |