Difference between revisions of "MBC1"

m (→Pinout) |

|||

| Line 2: | Line 2: | ||

= MBC1 = | = MBC1 = | ||

| + | |||

| + | Nintendo's MBC1 can be used to address up to 16 Mbit of ROM and 256 kbit of SRAM, depending on the mode MBC1 is set to. | ||

== Pinout == | == Pinout == | ||

| Line 80: | Line 82: | ||

{{clear|both}} | {{clear|both}} | ||

| + | |||

| + | == Registers == | ||

| + | |||

| + | |||

| + | Write-Accessible Registers: | ||

| + | |||

| + | * 0x0000-0x1FFF: RAM Enable register | ||

| + | * 0x2000-0x3FFF: ROM Bank register | ||

| + | * 0x4000-0x5FFF: RAM Bank register | ||

| + | * 0x6000-0x7FFF: Mode register | ||

| + | |||

| + | === RAM Enable Register === | ||

| + | |||

| + | <pre> | ||

| + | XX XX XX XX D3 D2 D1 D0 0x00 @ reset | ||

| + | \_________/ | ||

| + | \-------- RAM Enable | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | A value of 0x0A enables SRAM access, all other values disable SRAM access. | ||

| + | |||

| + | === ROM Bank Register === | ||

| + | |||

| + | <pre> | ||

| + | XX XX XX D4 D3 D2 D1 D0 0x00 @ reset | ||

| + | \____________/ | ||

| + | \-------- ROM Bank | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | ROM Bank selects which bank is mapped to 0x4000-0x7FFF. The written value is zero-adjusted before output on RA18{{ndash}}RA14. | ||

| + | |||

| + | === RAM Bank Register === | ||

| + | |||

| + | <pre> | ||

| + | XX XX XX XX XX XX D1 D0 0x00 @ reset | ||

| + | \___/ | ||

| + | \----- RAM Bank | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | RAM Bank selects which bank is mapped to 0xA000-0xBFFF when in mode 4 MBit/256 kbit. When in mode 16 Mbit/64 kbit, it can be used to select the upper two ROM address lines. | ||

| + | |||

| + | === Mode Register === | ||

| + | |||

| + | <pre> | ||

| + | XX XX XX XX XX XX XX D0 0x00 @ reset | ||

| + | \/ | ||

| + | \--- Mode | ||

| + | |||

| + | </pre> | ||

| + | |||

| + | The mode bit switches between 16 Mbit ROM/64 kbit SRAM mode ('0') and 4 Mbit ROM/256 kbit SRAM mode ('1'). When in 16 Mbit/64 kbit mode, address lines AA14{{ndash}}AA13 switch according to A14. When in 4 Mbit/256 kbit mode, the upper address lines AA14{{ndash}}AA13 stay fixed regardless of A14. | ||

| + | |||

| + | == Behavior == | ||

| + | |||

| + | <pre> | ||

| + | |||

| + | </pre> | ||

= MBC2 = | = MBC2 = | ||

Revision as of 23:53, 26 May 2015

Contents

MBC1

Nintendo's MBC1 can be used to address up to 16 Mbit of ROM and 256 kbit of SRAM, depending on the mode MBC1 is set to.

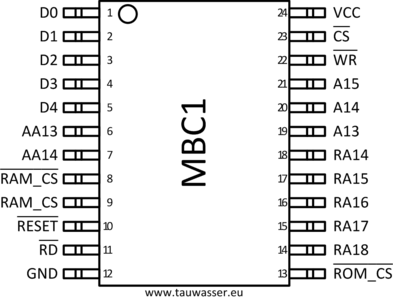

Pinout

| Pin No. | Name | Type | Comment |

|---|---|---|---|

| 24 | VCC | PWR | 5V supply |

| 14 | GND | PWR | Ground supply |

| 5Template:Ndash1 | D4Template:NdashD0 | I | Data Bus |

| 11 | RD | I | Low-Active Read Enable |

| 22 | WR | I | Low-Active Write Enable |

| 23 | CS | I | Low-Active Chip Select |

| 10 | RESET | I | Low-Active Asynchronous Reset |

| 21Template:Ndash19 | A15Template:NdashA13 | I | Address Bus |

| 18Template:Ndash14 | RA18Template:NdashRA14 | O | Upper ROM Address Lines |

| 7Template:Ndash6 | AA14Template:NdashAA13 | O | Upper ROM/RAM Address Lines |

| 8 | RAM_CS | O | Low-Active RAM Chip Select |

| 9 | RAM_CS | O | High-Active RAM Chip Select |

| 13 | ROM_CS | O | Low-Active ROM Chip Select |

Registers

Write-Accessible Registers:

- 0x0000-0x1FFF: RAM Enable register

- 0x2000-0x3FFF: ROM Bank register

- 0x4000-0x5FFF: RAM Bank register

- 0x6000-0x7FFF: Mode register

RAM Enable Register

XX XX XX XX D3 D2 D1 D0 0x00 @ reset

\_________/

\-------- RAM Enable

A value of 0x0A enables SRAM access, all other values disable SRAM access.

ROM Bank Register

XX XX XX D4 D3 D2 D1 D0 0x00 @ reset

\____________/

\-------- ROM Bank

ROM Bank selects which bank is mapped to 0x4000-0x7FFF. The written value is zero-adjusted before output on RA18Template:NdashRA14.

RAM Bank Register

XX XX XX XX XX XX D1 D0 0x00 @ reset

\___/

\----- RAM Bank

RAM Bank selects which bank is mapped to 0xA000-0xBFFF when in mode 4 MBit/256 kbit. When in mode 16 Mbit/64 kbit, it can be used to select the upper two ROM address lines.

Mode Register

XX XX XX XX XX XX XX D0 0x00 @ reset

\/

\--- Mode

The mode bit switches between 16 Mbit ROM/64 kbit SRAM mode ('0') and 4 Mbit ROM/256 kbit SRAM mode ('1'). When in 16 Mbit/64 kbit mode, address lines AA14Template:NdashAA13 switch according to A14. When in 4 Mbit/256 kbit mode, the upper address lines AA14Template:NdashAA13 stay fixed regardless of A14.